Лекции по схемотехнике, стр. 23

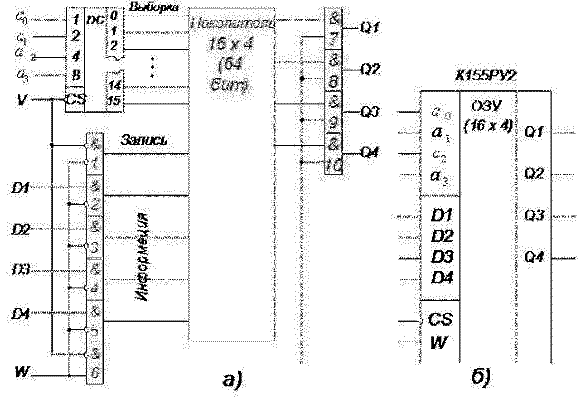

При CS=0 и W=1 формируется сигнал «Чтение» и информация из выбранной ячейки читается с выходов Q1…Q4.

Рисунок 70 МС К155РУ2: а) Структурная схема, б) Условное обозначение

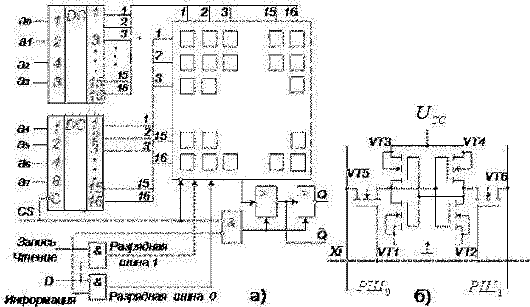

Микросхемы К176РУ2, К561РУ2 с организацией 256×1 изготовлены по технологии КМОП и представляют собой ЗУ со структурой 3D (Рисунок 71,а).

Рисунок 71 Микросхема К176РУ2: а) Структурная схема; б) Элемент памяти.

Структурная схема МС К176РУ2 приведена на рисунке 71,а. Схема содержит два дешифратора: DC столбцов и DC строк. Дешифраторы имеют по 4 входа, на которые подаётся по 4 разряда из общего 8-разрядного адреса, и по 16 выходов. Каждая ячейка памяти находится на пересечении строки и столбца, поэтому два дешифратора обеспечивают обращение к 16×16=256 элементам памяти.

Каждый элемент памяти представляет собой статический RS-триггер (рисунок 71,б). Триггер имеет два парафазных входа/выхода. С разрядными шинами РШ0 и РШ1 триггер соединён через ключи VT5 и VT6. По разрядным шинам к триггеру подводится при записи и отводится при считывании информация в парафазной форме представления по РШ1 своим прямым значением, а по РШ0 — инверсным.

В режимах «Запись» и «Чтение» при возбуждении строки сигналом выборки Xi=1, снимаемым с дешифратора адреса строк, ключи VT5 и VT6 открываются и подключают триггер к разрядным шинам.

При Xi=0 ключи закрыты и триггер отключён (изолирован) шин, а информация в них хранится.

При считывании информации ключи подключают элемент памяти к разрядным шинам, они принимают потенциалы выходов триггера и через устройство ввода/вывода передают их на выход микросхемы.

РШ охватывают все элементы одного столбца, а переходит в активное состояние только один ЭП, соответствующий выбранной строке. Из него и считывается информация.

Среди отечественных серий микросхем хорошо развитыми являются серии К537 технологии КМОП с информационной ёмкостью от 1024×1 (К537РУ1) до 8192×8 (К537РУ17) и К132 технологии n-МОП с информационной ёмкостью от 1024×1 (К132РУ2) до 65536×1 (К132РУ10).

Ориентировочные значения основных параметров ОЗУ различных технологий приведены в таблице 10.

Таблица 10 Значения основных параметров ОЗУ

| Информационная ёмкость, кбит | Время выборки, нс | Потребляемая мощность в режиме обращения, мкВт/бит | Технология |

|---|---|---|---|

| 64 | 2.7–15 | 0.02–0.5 | ЭСТЛ |

| 16 | 35–100 | 0.05–0.1 | ТТЛ |

| 16 | 100–200 | 0.03–0.05 | И²Л |

| 64 | 25–300 | 0.01–0.2 | n-МОП |

| 256 | 25–200 | 0.005–0.02 | КМОП |

| 16 | 1.7–4.5 | 0.1–0.2 | GaAs |

Список использованных источников

1 Быстров Ю.А. Электронные цепи и микросхемотехника: Учебник. – М.: Высш, шк., 2002. – 384 с.

2 Гусев В. Г. Электротехника и микропроцессорная техника: Учебник для вузов. – М.: Высшая школа, 2006. – 800 с.

3 Нарышкин А. К. Цифровые устройства и микропроцессоры: Учеб. пособие для студ. Высш. Учеб. Заведений – М.: Издательский центр «Академия» , 2006. – 320 с.

4 Новиков Ю. В. Введение в цифровую схемотехнику – М.: Интернет – Университет Информационных Технологий; БИНОМ. Лаборатория знаний, 2007. – 373 с.

5 Угрюмов Е. П. Цифровая схемотехника. – СПб. : БХВ – Петербург, 2001. - 528 с.

6 Цифровые и аналоговые интегральные микросхемы: Справочник / С. В. Якубовский, Л. И. Ниссельсон, В. И. Кулешова и др.; Под редакцией С. В. Якубовского, — М. : Радио и связь, 1989. – 496 с.